# Fabrication of the semiconductor substrate for electric and photonic integrated circuits by pattern SIMOX method

Thesis presented for the degree of

Doctor of Engineering

in

Electrical and Electric Engineering,

Graduate School of Science and Engineering,

Tokyo Institute of Technology

by

Koichiro Kishima

## Contents

| Chapter 1 Introduction                                                       | 5  |

|------------------------------------------------------------------------------|----|

| 1-1 Background                                                               | 5  |

| 1-2 Review of silicon photonics                                              | 6  |

| 1-3 Structures of SOI transistors and directional movement of SOI substrate  | 10 |

| 1-4 Purpose of research                                                      | 12 |

| 1-5 Framework of thesis                                                      | 14 |

| Chapter 2 Summary of SIMOX technology and position of this research          | 17 |

| 2-1 Introduction                                                             | 17 |

| 2-2 Fabrication methods of CMOS grade SOI substrate                          | 17 |

| 2-2-1 SmartCut method                                                        | 18 |

| 2-2-2 SIMOX method                                                           | 19 |

| 2-2-3 Selection of fabrication method for buried optical waveguide formation | 19 |

| 2-3 Review of SIMOX method for SOI substrate                                 | 20 |

| 2-4 Review of pattern SIMOX method                                           | 22 |

| 2-5 Optical waveguide fabrication by pattern SIMOX with transparent mask     | 25 |

| 2-6 Features of vertically stacked EPIC                                      | 27 |

| 2-7 Experiment of uniform SIMOX on flat SOI substrate                        | 29 |

| 2-7-1 Purpose of the experiment                                              | 29 |

| 2-7-2 Method of uniform SIMOX on flat SOI substrate                          | 30 |

| 2-7-3 Results of uniform SIMOX on flat SOI substrate                         | 30 |

| 2-8 Position of this research                                                | 34 |

| 2-9 Summary                                                                  | 34 |

| Chapter 3 Non-destructive defect pinpointing by fluorescent microscope       | 35 |

| 3-1 Introduction                                                             | 35 |

| 3-2 Existing defect examination method by fluorescent microscope             | 36 |

| 3-3 Deblurring technology with computational photography                     | 38 |

| 3-4 Proposed imaging method                                                                                                                                                                                                                                                                                | 40                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3-5 Experiment for verification                                                                                                                                                                                                                                                                            | 44                         |

| 3-5-1 Experimental setup and specimen                                                                                                                                                                                                                                                                      | 44                         |

| 3-5-2 Verification result                                                                                                                                                                                                                                                                                  | 46                         |

| 3-6 Scanning range and expanding method of scanning range                                                                                                                                                                                                                                                  | 51                         |

| 3-6-1 Applicable scanning range of proposed pinpointing method                                                                                                                                                                                                                                             | 52                         |

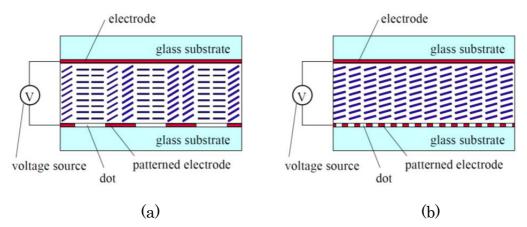

| 3-6-2 Expanding scanning range with liquid-crystal panel                                                                                                                                                                                                                                                   | 53                         |

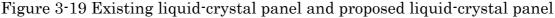

| 3-6-3 Proposed liquid-crystal panel for compensating spherical aberration                                                                                                                                                                                                                                  | 55                         |

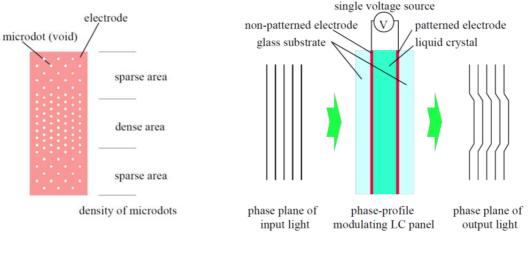

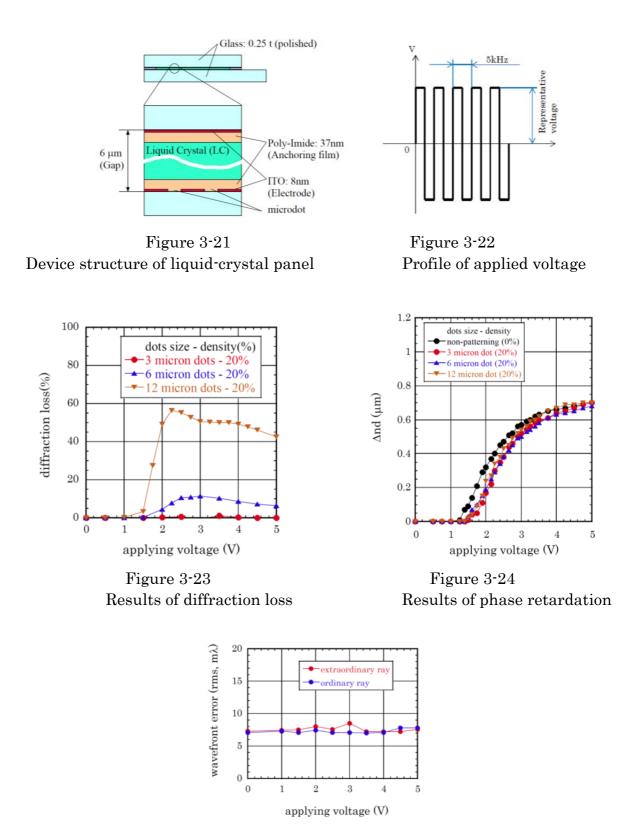

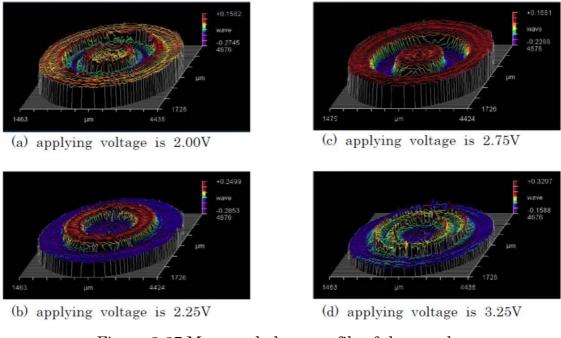

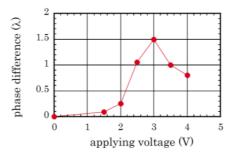

| 3-6-4 Experiment of phase modulation with proposed liquid-crystal panel                                                                                                                                                                                                                                    | 57                         |

| 3-6-5 Panel for compensating spherical aberration with proposed principles                                                                                                                                                                                                                                 | 60                         |

| 3-6-6 Amount of expanding scanning range by proposed liquid-crystal panel                                                                                                                                                                                                                                  | 61                         |

| 3-7 Application of non-destructive defect examination method                                                                                                                                                                                                                                               | 62                         |

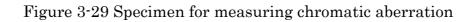

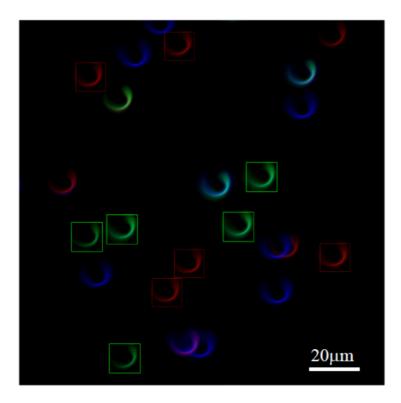

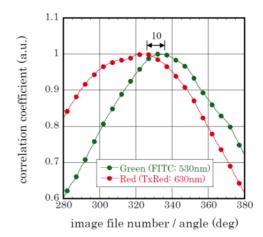

| 3-7-1 Measurement of chromatic aberration of optics                                                                                                                                                                                                                                                        | 62                         |

| 3-7-2 Measurement of 3D position of gene and distance between genes                                                                                                                                                                                                                                        | 65                         |

| 3-8 Summary                                                                                                                                                                                                                                                                                                | 68                         |

|                                                                                                                                                                                                                                                                                                            |                            |

| Chapter 4 Fabrication of buried optical waveguide by pattern SIMOX                                                                                                                                                                                                                                         | 69                         |

| 4-1 Introduction                                                                                                                                                                                                                                                                                           | 69                         |

| 4-2 Adoption of mask material for ion implantation                                                                                                                                                                                                                                                         | 70                         |

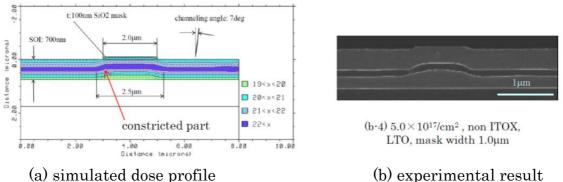

| 4-3 Applying device simulator to oxygen ion implantation                                                                                                                                                                                                                                                   | 70                         |

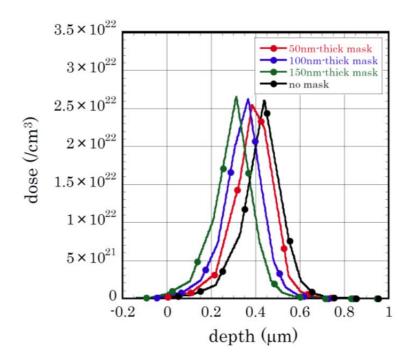

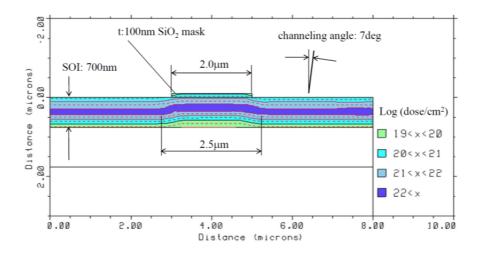

| 4-3-1 Adjustment of implantation function to oxygen ion implantation                                                                                                                                                                                                                                       | 71                         |

|                                                                                                                                                                                                                                                                                                            |                            |

| 4-3-2 Projection range and dose of implantation onto substrate with mask                                                                                                                                                                                                                                   | 73                         |

| 4-3-2 Projection range and dose of implantation onto substrate with mask<br>4-4 Specification of SOI substrate                                                                                                                                                                                             | 73<br>74                   |

|                                                                                                                                                                                                                                                                                                            |                            |

| 4-4 Specification of SOI substrate                                                                                                                                                                                                                                                                         | 74                         |

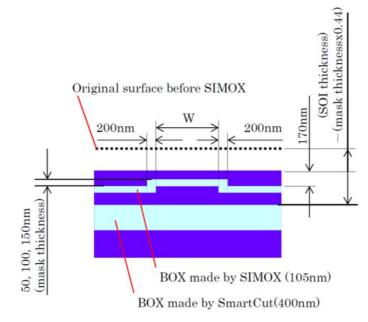

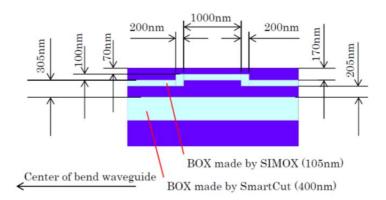

| <ul><li>4-4 Specification of SOI substrate</li><li>4-4-1 Structure of buried optical waveguide</li></ul>                                                                                                                                                                                                   | 74<br>74                   |

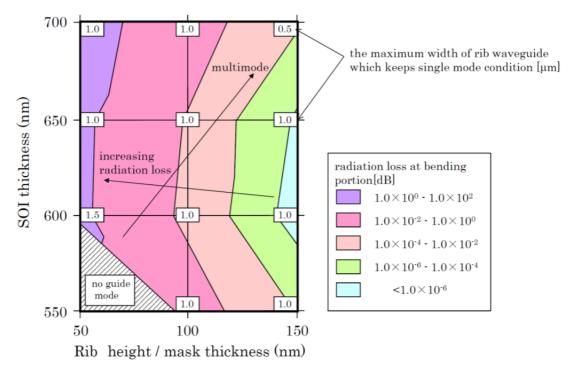

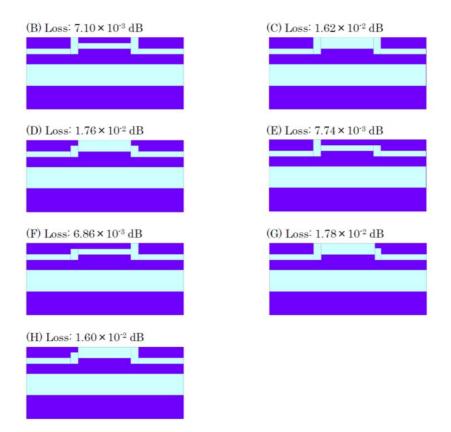

| <ul> <li>4-4 Specification of SOI substrate</li> <li>4-4-1 Structure of buried optical waveguide</li> <li>4-4-2 Reduction technique of radiation loss at bending waveguide</li> </ul>                                                                                                                      | 74<br>74<br>77             |

| <ul> <li>4-4 Specification of SOI substrate</li> <li>4-4-1 Structure of buried optical waveguide</li> <li>4-4-2 Reduction technique of radiation loss at bending waveguide</li> <li>4-4-3 Specification of SOI substrate</li> </ul>                                                                        | 74<br>74<br>77<br>79       |

| <ul> <li>4-4 Specification of SOI substrate</li> <li>4-4-1 Structure of buried optical waveguide</li> <li>4-4-2 Reduction technique of radiation loss at bending waveguide</li> <li>4-4-3 Specification of SOI substrate</li> <li>4-5 Pattern SIMOX fabrication under standard SIMOX conditions</li> </ul> | 74<br>74<br>77<br>79<br>80 |

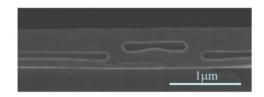

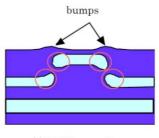

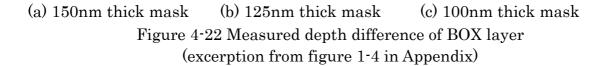

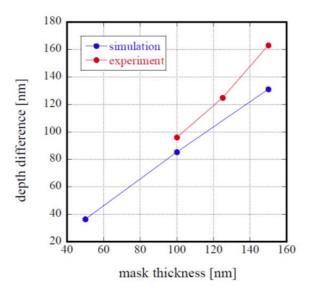

| 4-5-4 Discussions about thickness variation of BOX layer                   | 84  |

|----------------------------------------------------------------------------|-----|

| 4-5-5 Feedback of experimental results                                     | 85  |

| 4-6 Effect of ITOX annealing at standard dose condition                    | 86  |

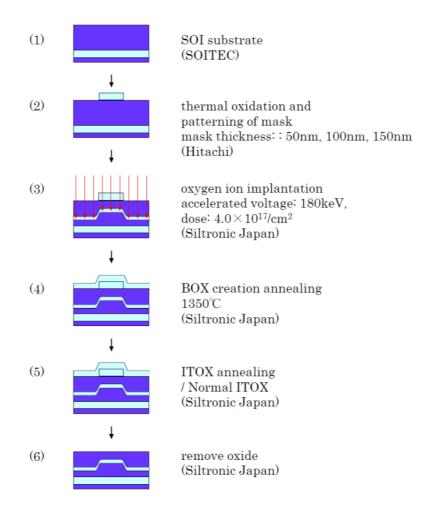

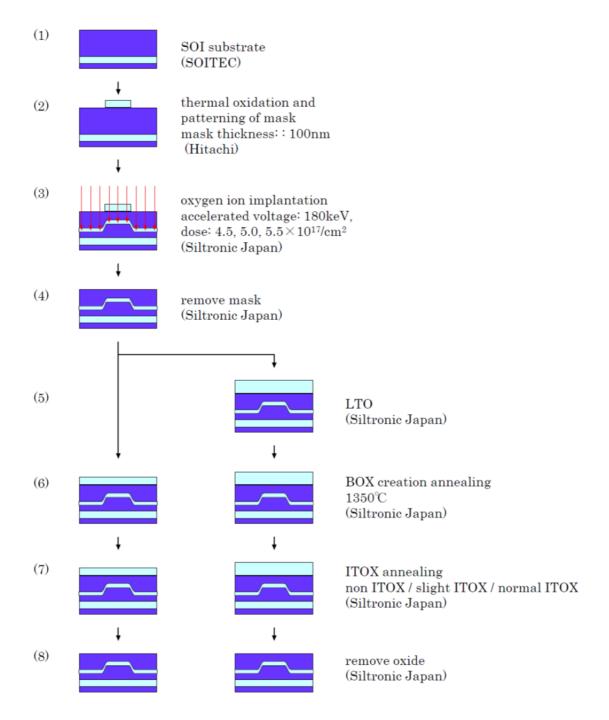

| 4-6-1 Process flow and its conditions                                      | 86  |

| 4-6-2 Discussion about cover layer (LTO)                                   | 88  |

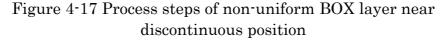

| 4-6-3 Discussions about discontinuity and thickness variation of BOX layer | 88  |

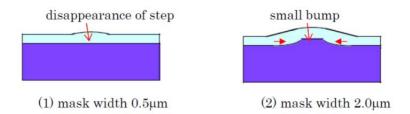

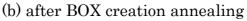

| 4-6-4 Discussions about step and uneven surface                            | 90  |

| 4-6-5 Discussions about influence on BOX layer made by SmartCut            | 92  |

| 4-6-6 Discussions about projection ranges related to mask thickness        | 93  |

| 4-6-7 Feedback of experimental results                                     | 94  |

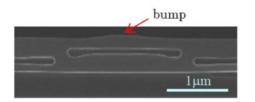

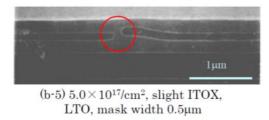

| 4-7 Pattern SIMOX with increasing dose                                     | 95  |

| 4-7-1 Process flow and its conditions                                      | 95  |

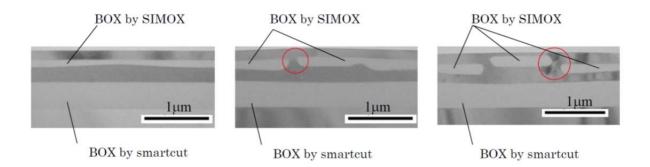

| 4-7-2 Discussions of continuity of BOX layer                               | 97  |

| 4-7-3 Discussion about asymmetry of BOX layer                              | 99  |

| 4-7-4 Discussion about silicon island                                      | 100 |

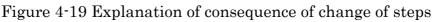

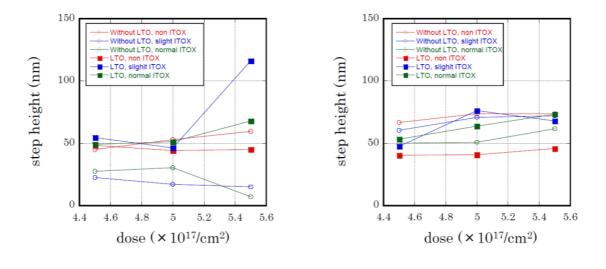

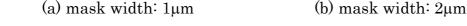

| 4-7-5 Discussion about surface flatness                                    | 100 |

| 4-7-6 Feedback of experimental results                                     | 103 |

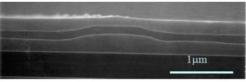

| 4-8 Optimization of pattern SIMOX                                          | 104 |

| 4-8-1 Reduction of asymmetry of BOX layer made by SIMOX                    | 105 |

| 4-8-2 Prevention of surface defects by remediation of material             | 106 |

| 4-8-3 Prevention of step formation by sputtering in ion implantation       | 107 |

| 4-8-4 Fabrication of buried waveguide by optimized pattern SIMOX           | 108 |

| 4-9 Application of buried optical waveguide made by pattern SIMOX          | 112 |

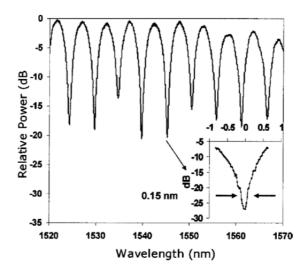

| 4-9-1 Low propagation loss optical waveguide                               | 112 |

| 4-9-2 Optical coupling                                                     | 113 |

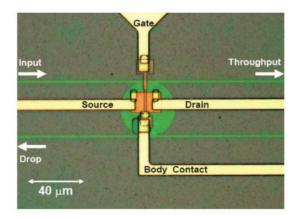

| 4-9-3 Fabrication of vertically stacked electric and photonic circuits     | 116 |

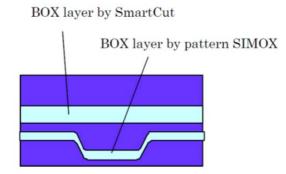

| 4-9-4 EPIC substrate with pattern SIMOX precedes SmartCut                  | 117 |

| 4-10 Summary                                                               | 118 |

|                                                                            |     |

|                                                                            |     |

| Chapter 5 Optical Memory with using 501 mansistor 115 | Chapter 5 Optical Memory with using SOI transistor | 119 |

|-------------------------------------------------------|----------------------------------------------------|-----|

|-------------------------------------------------------|----------------------------------------------------|-----|

| 5-1 Introduction                                                 | 119 |

|------------------------------------------------------------------|-----|

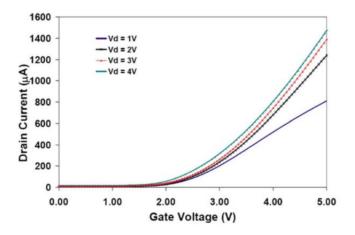

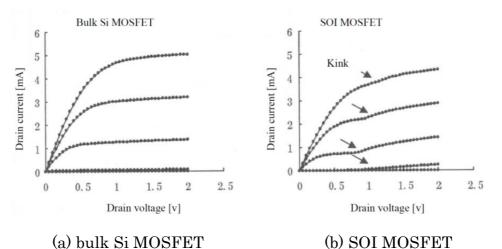

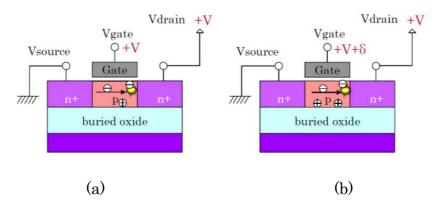

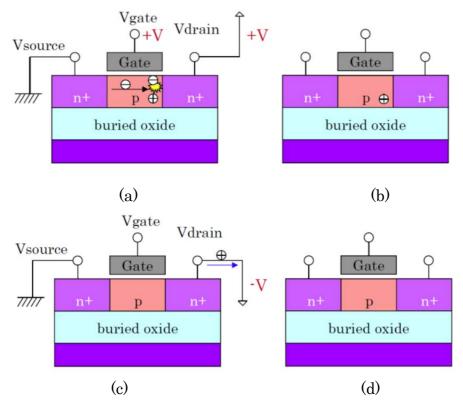

| 5-2 Floating body effect in SOI transistors                      | 120 |

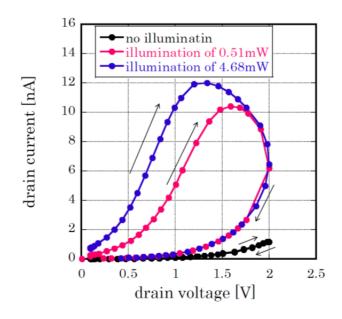

| 5-2-1 Kink effect in drain current-drain voltage relationship    | 120 |

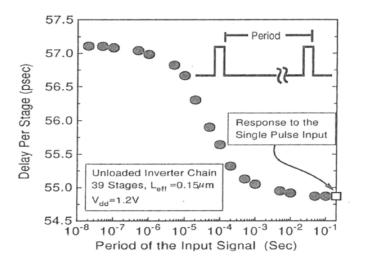

| 5-2-2 Instability of threshold voltage by history effect         | 122 |

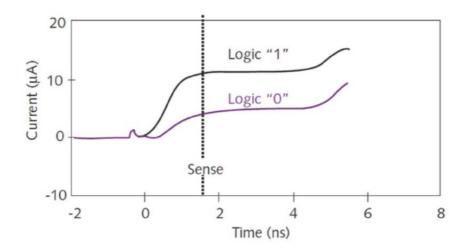

| 5-3 Memory device whose recording principle is impact ionization | 123 |

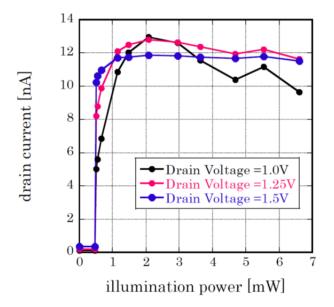

| 5-4 Memory device with two photon absorption                     | 125 |

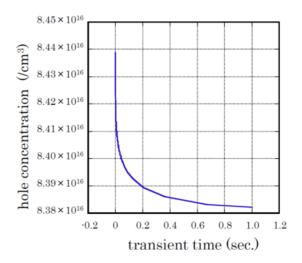

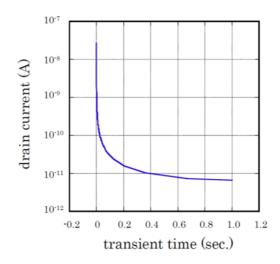

| 5-4-1 Simulation model                                           | 127 |

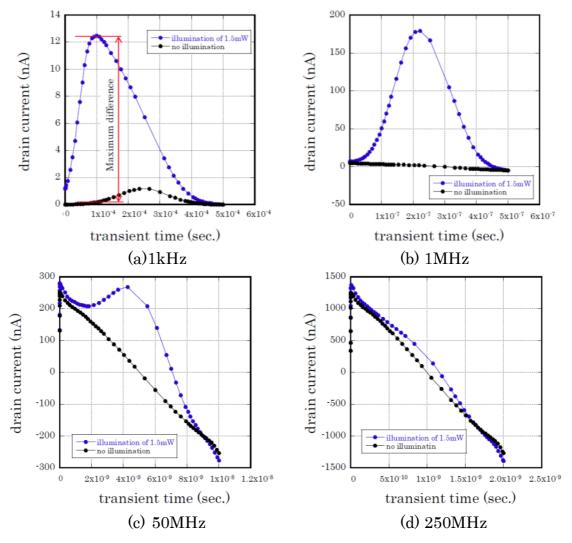

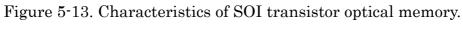

| 5-4-2 Simulation results                                         | 128 |

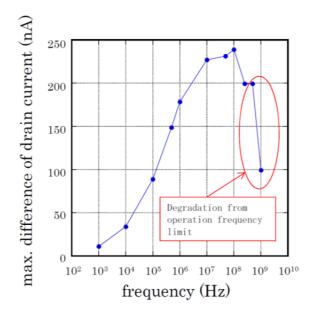

| 5-5 Operation of SOI transistor optical memory                   | 133 |

| 5-6 Configuration of SOI transistor optical memory               | 134 |

| 5-7 Summary                                                      | 138 |

| Chapter 6 Conclusion                                             | 139 |

| 6-1 Summary                                                      | 139 |

| 6-2 Future work                                                  | 141 |

| Appendix                                                         | 143 |

| Acknowledgements                                                 | 151 |

| References                                                       | 153 |

| Publication list                                                 | 164 |

| Papers on this thesis                                            | 164 |

| International conferences                                        | 164 |

| Japanese Conferences                                             | 165 |

| Related papers                                                   | 165 |

| Related presentations                                            | 166 |

| News Articles                                                    | 166 |

## Chapter 1 Introduction

#### 1-1 Background

Based on an analysis published in June 2011 by International Data Corporation [1], a global electrical data created in 2011 reaches to 1.8 zeta byte which is nine times compared to the data in 2006. The expected global electrical data created in 2016 is eight times of 2011. So the growing rate of electrical data will be sustained. Individual contribution including downloading from web site is 75% of created electrical data. This growth of electrical data by individual indicates further accession of network traffic to the home which is located at the terminal of communication network.

According to a report from Japanese Ministry of Internal Affairs and Communications published in May 2011[2], the rate of internet usage at home reaches to 77.9% in 2010. The rate of optical communication path to home is 52.2%. This data shows optical communication path already reaches to the terminal of communication network and increasing of the electrical data created by individuals. In addition, increasing of optical communication path at the terminal indicates market growth of short distance optical communication.

On the other hand, in case of enterprise communication, in "TSUBAME 2.0" a supercomputer at Tokyo Institute of Technology launched in 2010, optical communication between rack mounts enables faster calculation. This shows a market of short distance optical communication is also important in enterprise business.

The market growth of short distance optical communication requires not only high functionality but also low cost to optical communication devices.

Electronic Photonic Integrated Circuits: EPIC is expected as a technology which solves both high functionality and low cost of optical communication devices. The reason of the expectation is based on the history of integrate circuits which brought high functionality and low cost. The EPIC implements both electrical integrate circuits and optical circuits on a silicon substrate. EPIC can handle optical signals guided in an optical waveguide by adjacent electric devices, and can create optical signals from electric signals created on the same substrate. EPIC technology is based on the silicon photonics[4,5] which is optical waveguide circuits technology on silicon substrate, and CMOS (Complementary Metal Oxide Semiconductor) integrated circuits technology which is electric circuits technology on silicon substrate.

Comparing to CMOS integrated circuits technology which is mature technology with 15year precise technology roadmap by ITRS, silicon photonics is growing technology, so silicon photonics is needed to adjust to current CMOS integrated circuits technology in order to realize EPIC on silicon substrate.

This paper is related to a research of silicon waveguide technology which adjusts to CMOS integrated circuits technology.

In this chapter, silicon photonics technology will be reviewed, the purpose of this research is described, and a structure of this paper is shown.

## 1-2 Review of silicon photonics

Silicon photonics is a collective term of optical waveguide devices made on silicon substrate. And recently silicon photonics has many research activities. Silicon photonics uses two major characteristics of silicon material, the first characteristic is silicon is transparent for the light whose wavelength is longer than 1.1  $\mu$ m, and the second characteristic is silicon dioxide is also transparent and has lower index than silicon. As a result, silicon photonics can attain well confined optical waveguide structure for 1.3 $\mu$ m and 1.5 $\mu$ m light utilized in optical communication systems brought by large relative index difference between silicon and silicon dioxide. The well confined optical waveguide structures can be manufactured at lower cost with using semiconductor facilities for VLSI.

The history of silicon photonics was started by R. A. Sorel and K.

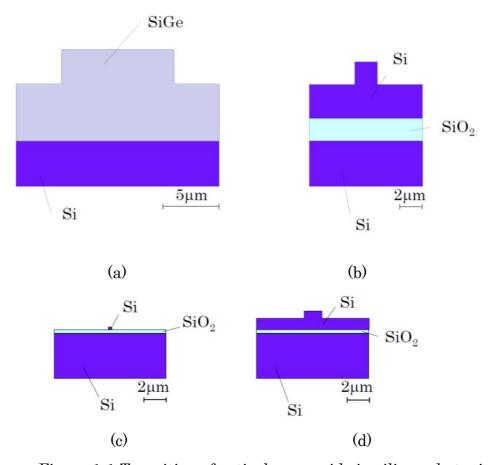

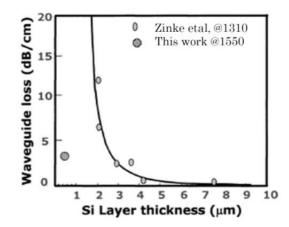

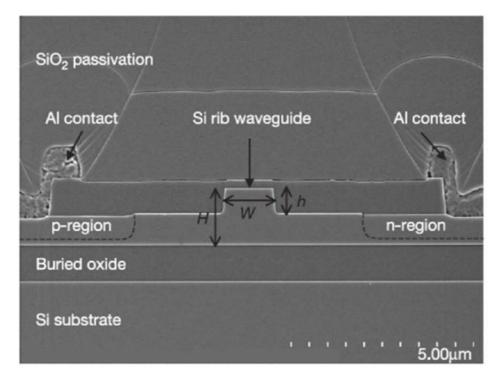

Petermann [6-8] at the end of 1980s and the beginning of 1990s. At these years several material combinations were used, they are high-resistivity epitaxial silicon layer on highly doped silicon substrate (relative index difference  $\Delta n=0.009$ )[6], Ge-Si epitaxial layer on silicon substrate (relative index difference  $\Delta n=0.1$ )[8], and silicon bonded layer on silica substrate (relative index difference  $\Delta n=2.05$ )[8]. The most of research activities in these years were focused on optical waveguide characteristics. The representative of optical waveguide structure[6] in these years is shown in figure 1-1(a). The thickness of Si-Ge layer is 7µm and rib height and width are 2.8µm and 10µm respectively.

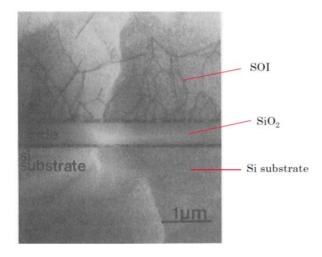

At the latter 1990s, research activities using SOI (Silicon-on-Insulator) substrate which has buried oxide (BOX) layer were started[9-11], and researches on passive functional optical waveguide devices were appeared, for example, they are optical star coupler [12] and phased-array wavelength multi-demultiplexer [13]. But SOI substrates in these researches[9-13] are BE-SOI (bond and etchback silicon-on-insulator) substrates, so surface silicon layer has 5-11 $\mu$ m thick. The single mode optical waveguide condition can be realized only with rib waveguide structure having silicon dioxide clad layer. In addition the minimum width of optical waveguide is 2 or 3 $\mu$ m, so propagating optical light is not well confined. The representative of optical waveguide structure[9] in these years is shown in figure 1-1(b).

Between latter 1990s and 2000, SmartCut [14] and SIMOX[15] were developed which are fabricating technologies of BOX substrates for VLSI. As SOI substrate fabricated by SmartCut or SIMOX with thin silicon layer in the range from 0.1µm to 1µm and with high quality began to supply, characteristics of electrical circuits and optical waveguide devices were rapidly upgraded. In the field of electrical circuits with SOI substrate, PowerPC processor is manufactured by IBM from 2000[16]. In 2005 when the game machine: Playstation3 using Cell Processor developed by 3 company-collaboration (IBM, Toshiba, and Sony) was launched, the mass-production technology of CMOS LSI circuit on 300mm SOI substrate had been completed. In the field of optical waveguide devices with SOI substrate, strip-type waveguide called "silicon wire" realized well confined optical waveguide brought by large relative index difference between silicon and silicon dioxide appeared, and passive type optical filter device with microring resonator made of very small cross-section of  $0.4\mu m \ge 0.2\mu m$  and  $2.5\mu m$  radius waveguide were reported[18]. The single mode conditions of strip type optical waveguide were reported that the crosssection of waveguide is less than  $0.3\mu m \ge 0.3\mu m \ge 0.5\mu m \ge 0.2\mu m$  is single mode condition.

On the other hand, research activities on optical waveguide with nonlinear effect like Raman laser [21, 22] appeared with using precise fabrication technology and high quality silicon layer.

In the aspect of a function of optical waveguide device, researches in optical modulator went ahead compared to researches in emitting device and detector. Lipson reported optical light modulator with pn structure in microring resonator[23]. In 2005, Intel reported Mach-Zehnder type optical light modulator operated at 10GHz[24]. Reed demonstrated 50GHz operation in Carrier-depletion type optical modulator[25]. And Enablence reported optical communication device with Mach-Zehnder interferometer[26].

The optical waveguide structure is not only strip type[18, 23] shown in figure 1-1(c), but also ridge type[21, 22, 24, 26] shown in figure 1-1(d). The different waveguide structure is used for each application.

Figure 1-1 Transition of optical waveguide in silicon photonics.

(a) R. Soref and J. Lorenzo in 1986[6], (b)P. D. Trinh, etal in 1995 [9]

(c) K. Yamada, etal in 2003 [18], (d) L. Liao, etal in 2005 [24]

Regarding light detector, with research activities on forming Ge layer on silicon substrate in latter 2000s[27, 28], the characteristics of Ge light detector has great improvement in frequency response and sensitivity in this 5 years[29, 30]. Kotura reported Ge detector with 1.1A/W sensitivity and 32GHz (-3dB) frequency response at 1.55µm wavelength in 2009[31], so Ge type light detector is close to practical use.

On the other hand regarding light emitting devices, research activities using Ge material are also rapidly progressing. Kimerling reported direct-gap photoluminescence[32] and electroluminesence[33] using Ge material in 2009, and photoexcited type 1.59-1.61µm laser in 2010. So current injected type laser is thought to be reported soon. There is another research activity using hybrid structure made of silicon and group III-V compound material that is already commercialized as independent laser devices with higher emitting efficiency.

Bowers of University California, Santa Barbara applied bonding technology of group III-V compound laser on silicon substrate and introduced the light from the laser into optical waveguide in silicon layer[35], and demonstrated the wavelength-variable laser tuned by Bragg reflector in 2008[36].

In 2006, the combination with CMOS integrated electrical circuits and optical waveguide on SOI substrate was reported by Luxtera as optical communicating device[37]. This result was the first demonstration of EPIC. The demonstration of 40GHz optical transceiver was also reported by Luxtera with the combination of 130nm rule CMOS circuits and optical waveguides[38]. This optical transceiver device had no laser devices but had 40GHz optical modulators and optical detectors.

In latter 2000s two decade old from Soref's papar in 1986, silicon photonics had many type of candidate devices. At present, preparing of combination of CMOS circuits is going.

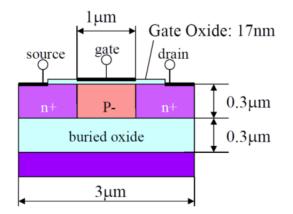

#### 1-3 Structures of SOI transistors and directional movement of SOI substrate

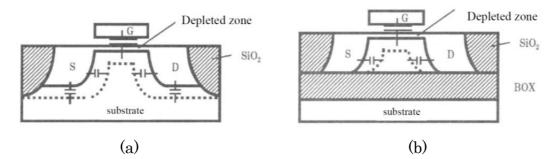

Because transistors fabricated on SOI substrate are electrically isolated by BOX layer from substrate, performance of the transistor is faster than transistors on bulk silicon substrate owing to small floating capacitance. In addition, power consumption of the transistor on SOI is smaller owing to small leak current to substrate[16].

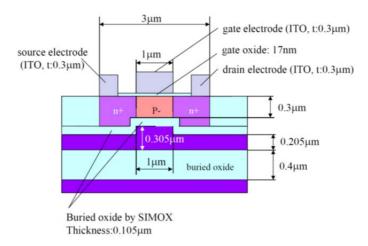

There are two types of transistor on SOI substrate, one is partially depleted-SOI (PD-SOI) and another is fully depleted-SOI (FD-SOI)[15]. The difference between two types is in depleted region. In FD-SOI transistor, the all area of body portion from just beneath gate oxide to boundary of BOX layer is depleted at operation. In PD-SOI transistor, partial area of body near gate oxide portion is depleted at operation. Reference 15 defines that PD-SOI transistors are made on the SOI whose top silicon layer has 80-200nm thick, and FD-SOI transistors are made on the SOI whose top silicon layer has 60-80nm thick.

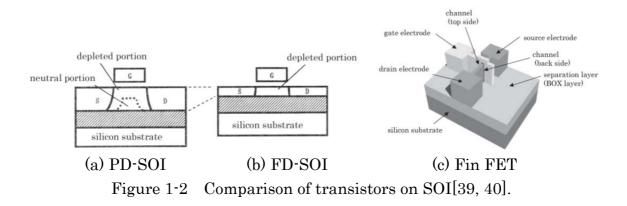

Recently, Fin-FET transistor whose operating speed is faster than FD-SOI or PD-SOI was reported[39]. Figure 1-2 shows the structures of transistor on SOI[39, 40]. In Fin-FET, BOX layer acts as separation layer and the direction of electric field is parallel to in-plane direction of SOI substrate. As shown in figure 1-2, there is a huge difference in structure between transistor types.

There is no need to say, bulk silicon substrate is common for all type of transistors fabricated on bulk silicon substrate despite the progress of design rule. But in the technology of PD-SOI and FD-SOI, thinner surface silicon layer is required as the progress of design rule[41, 42]. Luxtera used SOI substrate whose surface silicon layer is 220nm thick, and the thickness of 220nm is suitable thickness of 130nm design node of PD-SOI by Freescale Semiconductor, Inc. So thinner thickness of surface silicon layer is required when shorter gate length is applied. In FD-SOI, the thickness of surface silicon layer is required to be less than 10nm when the gate length is shorter than 30nm[42]. In Fin-FET 15nm is the suitable thickness of surface silicon layer in currently developed Fin-FET whose gate length is 20nm.

From the aspect of the characteristics of transistor fabricated on SOI,

directional movement of SOI is thinner thickness of surface silicon layer.

## 1-4 Purpose of research

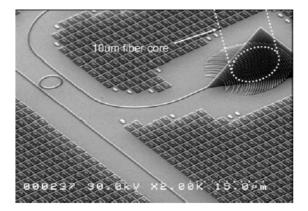

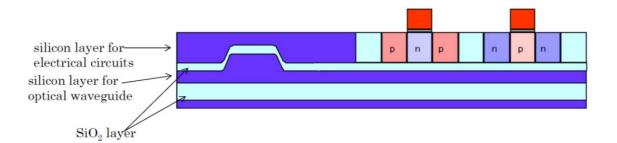

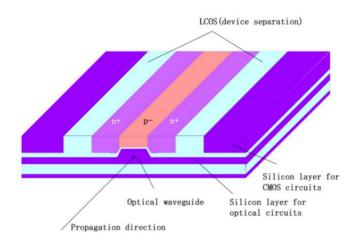

EPIC on silicon substrate is regarded as the best device for coding and decoding signal processing including advanced scrambling with a secret code at low cost because the signal processing is performed at the closest portion to optical waveguide on the same silicon substrate. Figure 1-3 shows the photograph of Luxtera's EPIC device[37]. Figure 1-4 shows the conceptual diagram of the devices. As shown in figures 1-3 and 1-4, silicon layer of electrical circuits and silicon layer of optical waveguide are same. The silicon layer is required to be divided into electrical circuit area and optical waveguide area with enough buffer area. By adding optical waveguide, the area of electrical circuits is reduced by area of optical waveguide and the buffer area.

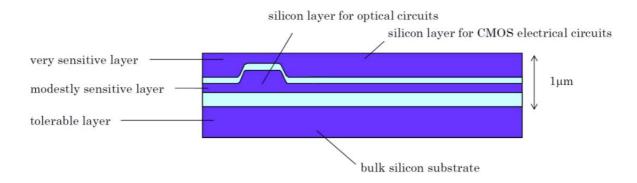

As mentioned above, surface silicon layer of 220nm thick is suitable for the thickness of CMOS circuits with 130nm node PD-SOI and single mode condition of well confined silicon wire optical waveguide with 400-500nm width. The additional process such as epitaxial growing on optical waveguide area might be required in order to obtain well confined condition when thinner surface silicon layer is applied suitable for narrower design rule in CMOS circuits.

Figure 1-3 Photographs of Luxtera's EPIC[37].

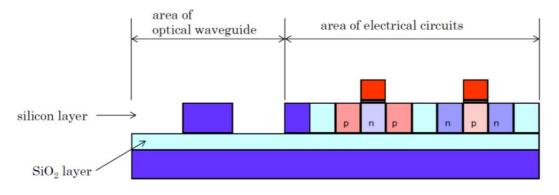

Figure 1-4 Conceptual diagram of Luxtera's EPIC. Electrical circuits and optical waveguide are fabricated on same silicon layer

The author proposed the EPIC structure that optical waveguide is fabricated on the second silicon layer from the surface and reduction of electric circuit area is to be minimum by the separation of layers of electrical circuits and optical waveguide. The proposed EPIC structure is shown in figure 1-5. In the proposed EPIC structure, there is no need to coincide thickness of silicon layer of electrical circuits and thickness of silicon layer of optical waveguide. It has the characteristic of availability that thickness of silicon layers can be suited for electrical circuits and optical waveguide independently.

Figure 1-5 Conceptual diagram of proposed EPIC. Electrical circuits and optical waveguide are fabricated in different silicon layer

The main purpose of this research is to establish fabricating technology of optical waveguide on the second layer from the surface by pattern SIMOX as a

compatible technology with CMOS electrical circuit technology. And technology of the pointing depth of defect suitable for total inspection is proposed and demonstrated as a required technology in fabrication of electrical circuits on the surface silicon layer. In addition as required in design process of integrated circuits of electrical circuits and optical waveguide circuits, the interaction of electrical device and optical device is scientifically clarified in order to establish the electrical and photonic integrated circuits on SOI substrate technology made by pattern SIMOX.

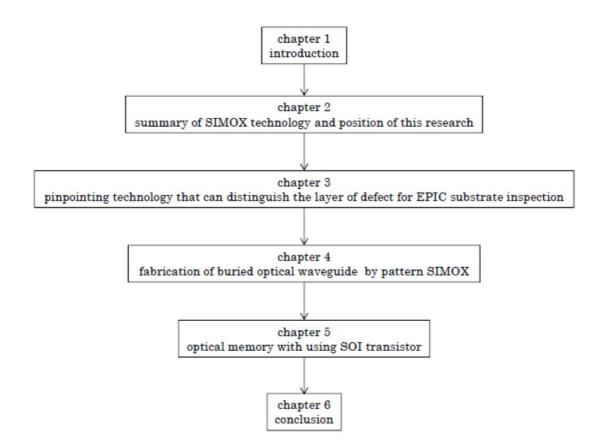

## 1-5 Framework of thesis

Framework of this thesis is shown in figure 1-6.

In chapter 1, requirement of optical communication device is not only high functionality but also low cost because of business expansion of short distance optical communication as a background of this research, and EPIC is expected as the technology which solves both requirements of optical communication devices. The main purpose of this research is described to establish fabricating technology of optical waveguide on the second layer from the surface by pattern SIMOX as a compatible technology with CMOS electrical circuit technology.

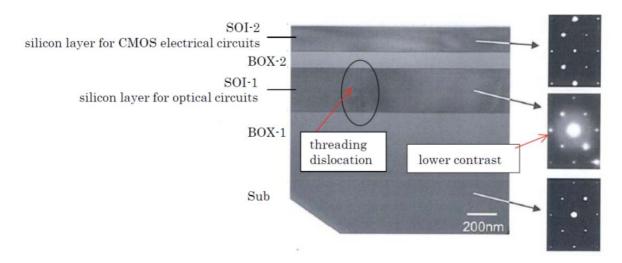

In chapter 2, SIMOX technology that is a fabrication technology of current CMOS grade SOI substrate is summarized, and results of fundamental examination are shown. The reason of application of pattern SIMOX in this research is described and positioning of this research is clearly shown with the analysis of the previous research on pattern SIMOX. From examination of SIMOX process to SOI substrate, characteristic of SOI substrate with double BOX layer made by SIMOX that there are defects in second silicon layer from the surface despite no defects in surface silicon layer is shown.

In chapter 3, research of non-destructive and effective defect pinpointing technology that can distinguish the defect position among surface silicon layer for electrical circuits, second silicon layer for optical circuits, and bulk silicon layer is described. Although the amount of 9TB in data size is created by existing optical defect inspection with fluorescent microscope is implemented on a 300mm silicon substrate, the proposed method can reduce the data size to from 1/10 to 1/20 despite 100nm depth resolution.

In chapter 4, research of pattern SIMOX technology to fabricate optical waveguide in second silicon layer in keeping with enough quality of surface silicon layer for CMOS electrical circuits is described. The process flow of SIMOX buried optical waveguide compatible with CMOS electrical circuits on surface layer is obtained. Through this research, phenomena that defects are created when buried oxide layer is separated and buried oxide profile coincide to ion implantation profile is successfully created by blocking the oxide in annealing process from the ambient are obtained.

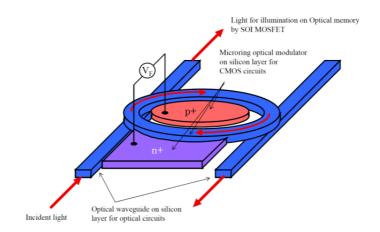

In chapter 5, research on the device using interaction between vertically stacked SOI transistor and optical waveguide is described. The SOI transistor memory device with two-photon absorption by illumination of 1.55µm light on body portion, residual hole at body portion, and floating body effect is proposed and validated.

In chapter 6, the thesis is concluded. The available configuration of electrical and photonic integrated circuits is disclosed and applications of obtained technologies through this research are described.

Figure 1-6 Framework of this thesis.

Chapter 2 Summary of SIMOX technology and position of this research

## 2-1 Introduction

In this chapter, two manufacturing methods of SOI substrate for CMOS electrical circuits are summarized in order to accomplish the research purpose of this research "to establish fabricating technology of optical waveguide on the second layer from the surface by pattern SIMOX as a compatible technology with CMOS electrical circuit technology". The reason of application of pattern SIMOX in this research is described. The pattern SIMOX technology to fabricate optical waveguide in second silicon layer in keeping with enough quality of surface silicon layer for CMOS electrical circuits is proposed through the analysis of the previous research on SIMOX and pattern SIMOX. From examination of SIMOX process to SOI substrate, characteristic of SOI substrate with double BOX layer made by SIMOX is studied. The obtained result is that there are defects in second silicon layer from the surface despite no defects in surface silicon layer. Small defects are negligible for optical circuits but are not negligible for electrical circuits because of device size. Because the distance between silicon layers of electrical circuits and optical circuits is less than 1µm, the requirement of non-destructive and effective defect pinpointing technology that can distinguish the defect position between two silicon layers is clarified. The positioning of this research is clearly shown by defining challenges in this research.

#### 2-2 Fabrication methods of CMOS grade SOI substrate

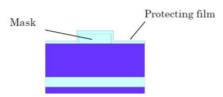

To fabricate optical waveguide underneath the surface, patterning of silicon dioxide is required. The patterning method of silicon dioxide is required to be CMOS compatible because CMOS transistors are fabricated at the surface silicon layer. As of 2011, there are only two fabrication methods that creates buried silicon dioxide layer, they are SmartCut method[14] and SIMOX method[15]. In this section, two fabrication methods are summarized and discussed regarding to the application in this research.

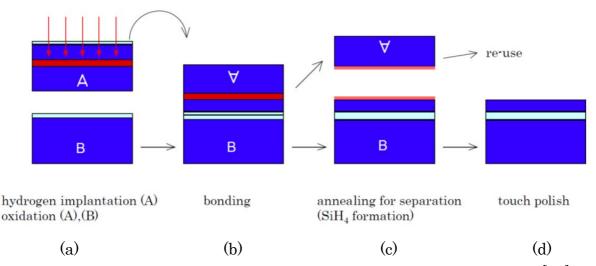

## 2-2-1 SmartCut method

Process of SmartCut is shown in figure 2-1. This method uses two silicon bulk substrates A and B. (a) Hydrogen ion implantation is performed to one bulk silicon substrate A. And subsequently thermal oxidation on two substrates A and B is performed for wafer bonding. (b) Wafer bonding process is performed. (c) Wafer separation process that includes precipitation of implanted hydrogen and creation of SiH<sub>4</sub>. Because SiH<sub>4</sub> is gas state, substrate separation is caused at the depth of hydrogen implantation. (d) Touch polishing is performed to obtain enough smooth surface for CMOS electrical circuits. In addition, substrate A can be reused.

Figure 2-1 Fabrication method of SOI for CMOS grade 1; SmartCut [14].

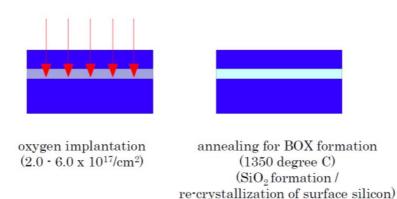

## 2-2-2 SIMOX method

The process of SIMOX is shown in figure 2-2. SIMOX SOI substrate is composed of one silicon bulk substrate. (a) Oxygen Ion implantation is performed. Dose of oxygen is much larger than dose of hydrogen in SmartCut process. And oxygen has larger atomic weight than hydrogen. Crystalline properties are almost lost at the passing area of oxygen ion after ion implantation. (b) The high temperature annealing between 1300 and 1350 degree C creates SiO<sub>2</sub> layer near ion implantation area and recovers crystalline properties of silicon by re-crystallization.

(a) (b) Figure 2-2 Fabrication method of SOI for CMOS grade 2; SIMOX method[15].

## 2-2-3 Selection of fabrication method for buried optical waveguide formation

From the aspect of optical waveguide beneath surface of silicon substrate, two methods are compared. In case optical waveguide is composed of two pure material; silicon and silicon-dioxide, the sub-micron range thickness modulation of silicon layer is required in order to make rib waveguide or strip waveguide. Because SmartCut requires flat surface at the bonding process, buried oxide layer must be flat. The thickness modulation portion should be made at the surface. Consequently, the flat surface cannot be obtained if we select SmartCut method. For this reason, SIMOX method is selected for buried optical waveguide formation beneath the surface, and the fabrication of SOI substrate which can integrate both electrical devices and optical devices is investigated in this research.

#### 2-3 Review of SIMOX method for SOI substrate

The acronym of SIMOX (Separation by implanted oxygen) was named by Izumi of NTT. In Izumi's paper[43] published in 1978, oxygen ion implantation to bulk silicon substrate was performed at 150keV and following high temperature annealing at 1150 degree C creates SOI substrate with buried SiO<sub>2</sub> layer (BOX: Buried Oxide), and operation of ring oscillator circuit using CMOS transistors was demonstrated. Results on SIMOX before 1980s including Izumi's work were summarized by P.L.F. Hemment of University of Surrey in 1986[44]. Dose value of ion implantation in these results are  $1.0 - 2.0 \times 10^{18}$ /cm<sup>2</sup>, are twofold of current dose.

Through researches acceleration of extensive on voltage ion implantation [45, 46], on dose value [47], and out-diffusion and in-diffusion of oxygen in annealing process[48], several optimized SIMOX conditions supposed for sophisticated CMOS circuits were obtained from 1990s to 2000. P.L.F. Hemment of University of Surrey reported the conditions of dose of 3.3 x 10<sup>17</sup>/cm<sup>2</sup> at acceleration voltage of 70keV[49]. Meng Chen of Chinese Academy of Science reported the conditions of dose of  $4.5 - 5.5 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 160keV[50] and reported that there was optimum condition in the range of dose of  $2.5 - 5.5 \ge 10^{17}$ /cm<sup>2</sup> by adjusting accelerated voltage[51]. Ogura of NEC reported high-quality SOI substrate with low defects density could be obtained at dose of  $2.0 - 6.0 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 180keV by applying the optimized annealing process[52]. Ibis Technology Corporation who is the manufacture of specialized ion implantation machine for SIMOX and Mitsubishi Material

Corporation jointly reported the conditions of dose of  $4.0 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 175keV[53] and conditions of dose of  $2.0 - 2.5 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 65keV[54, 55]. They launched the mass production of SOI substrate for CMOS integrated circuits. SIMOX methods for high quality SOI substrate with low defects density at dose of  $2.0 - 6.0 \ge 10^{17}$ /cm<sup>2</sup> are categorized into low-dose SIMOX method, and SIMOX methods at dose of  $1.0 - 2.0 \ge 10^{18}$ /cm<sup>2</sup> summarized by P.L.F. Hemment [44] categorized into high-dose SIMOX method[15].

Izumi of NTT reported a method to increase the thickness of buried oxide (BOX) layer by annealing at high concentration of oxygen, named ITOX (internal thermal oxidation), and reported the condition of dose of 4.0 x  $10^{17}$ /cm<sup>2</sup> at acceleration voltage of 180keV + ITOX[56]. Matsumura of Siltronic Japan reported that ITOX method was able to widen the dose condition to 3.0 - 4.0 x  $10^{17}$ /cm<sup>2</sup> at acceleration voltage of 180keV[57]. And Siltronic Japan started the mass production of SOI substrate for CMOS integrated circuits.

In the mass production of SOI substrate by SIMOX method, ITOX method is effective because ITOX reduces the operation time of ion implantation machine which is the most expensive among mass production machines of SIMOX method.

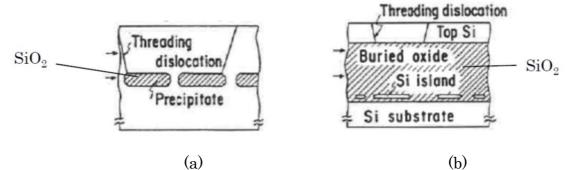

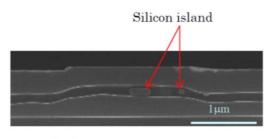

Figure 2-3 shows the defect types of buried oxide (BOX) layer of SOI substrate fabricated by SIMOX method. Figure 2-3(a) shows the discontinuity of BOX layer caused when insufficiency of dose at ion implantation or existence of particles on the surface at ion implantation. Figure 2-3(b) shows residual silicon portion in BOX layer called silicon island caused when excess of dose at ion implantation. Both defect types might bring degradation of insulating performance of BOX layer.

Figure 2-3 Defect types of buried oxide (BOX) layer by SIMOX method[47]

By summarizing the above reviews of SIMOX method, several optimized SIMOX conditions exist for SOI substrate with uniform BOX layer by applying uniform ion implantation. In the range of dose of  $2.0 - 6.0 \ge 10^{17}$ /cm<sup>2</sup>, optimized SIMOX conditions of SOI substrate for sophisticated CMOS circuits are expected by adjusting accelerated voltages and annealing process.

## 2-4 Review of pattern SIMOX method

In this section, previous researches of SIMOX method with partial ion implantation of oxygen called pattern SIMOX method or local SIMOX are summarized.

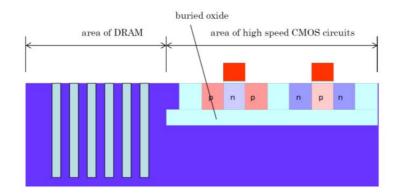

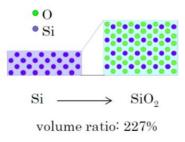

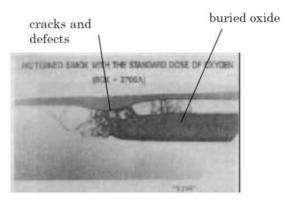

The purpose of obtaining local SOI substrate by pattern SIMOX method is integration of arithmetic circuits with CMOS on SOI and DRAM which is cheap data memories on bulk silicon substrate. The most popular and cheapest DRAM used in semiconductor field is capacitor type memories. The capacitor type memories apply the structure of fine and deep hole with oxide film and electrode on side wall of the hole on bulk silicon substrate for larger capacitance at small foot print to have higher performance of long-term recording and recording density. It is impossible to apply high-density capacitor type DRAM memories on SOI substrate because of existence of insulating BOX layer. From this reason, as shown in figure 2-4, the integration of arithmetic circuits with CMOS on SOI and DRAM by applying pattern SIMOX was attempted. The beginning of the attempt was reported by P.L.F. Hemment of University of Surrey in early 1990s[58, 59] before mass production of SOI substrate for CMOS integrated circuits. Fraunhofer Institute[60] and IBM[61] reported attempt of pattern SOI in about 2000. Despite these attempts, cracks at the boundary of ion implantation area were unavoidable because the volume increases of 2.27 times when silicon changes to silicon dioxide as shown in figure 2-5. Figure 2-6 shows the crack at the boundary of ion implantation reported by IBM[61].

Figure 2-4 Pattern SOI substrate attempted by pattern SIMOX[58-61]

Figure 2-5 Volume expansion when silicon changes to silicon dioxide

Figure 2-6 Experimental result of pattern SIMOX by IBM[61]

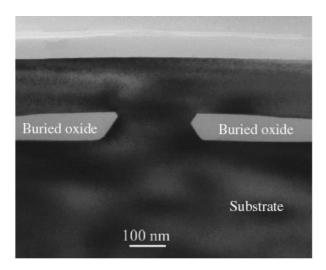

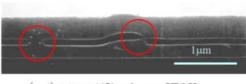

Mang Chen of Chinese Academy of Science reported two SIMOX conditions of dose of  $2.0 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 50keV[62] and dose of  $3.5 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 100keV[63] which avoid crack at the boundary of ion implantation. Figure 2-7 shows the experimental results by SIMOX condition of dose of  $3.5 \ge 10^{17}$ /cm<sup>2</sup> at acceleration voltage of 100keV[63]. From this picture the BOX layer is not symmetric, so created BOX layer does not reflect profile of ion implantation correctly.

Figure 2-7 Experimental result of pattern SIMOX by Meng Chen [63]

By summarizing the above reviews of pattern SIMOX method, partial and non-uniform ion implantation produces crack or uncontrollable BOX shape at the

boundary of ion implantation area. It is supposed to be very difficult to fabricate low defects SOI substrate for partial and non-uniform ion implantation SIMOX method.

## 2-5 Optical waveguide fabrication by pattern SIMOX with transparent mask

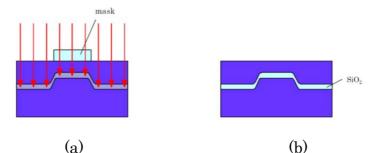

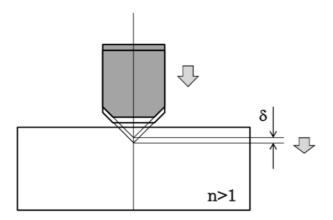

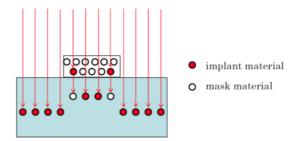

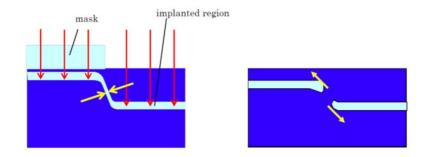

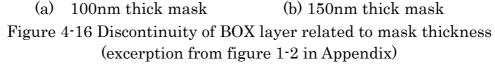

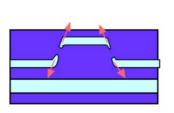

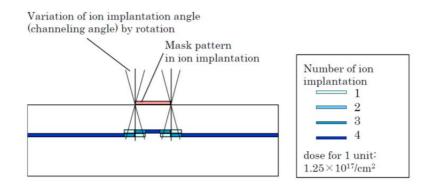

From the reviews of previous research of pattern SIMOX, partial and non-uniform dose ion implantation cannot create BOX layer reflected ion implantation profile correctly without defects[60-63]. In this thesis, optical waveguide fabrication by pattern SIMOX with transparent mask is proposed. This proposal is derived from the reason that uniform dose ion implantation at modulated depth reduces the stress by volume expansion of silicon to silicon dioxide and correct reflection of ion implantation fabricates optical waveguide underneath the surface by applying the transparent mask in ion implantation. Simplified process flow of the proposed method is shown in figure 2-8. Figure 2-8(a) oxygen ion implantation is performed through transparent patterned mask. Figure 2-8(b) high temperature annealing creates BOX layer with depth modulation.

Figure 2-8 Proposed pattern SIMOX method with transparent mask

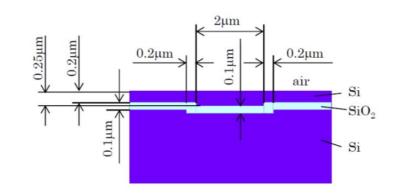

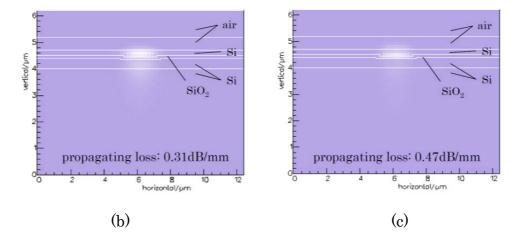

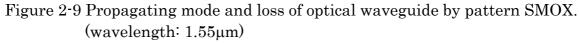

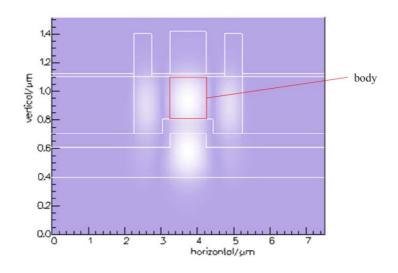

Properties of optical waveguide fabricated by pattern SIMOX method with transparent mask are discussed. Figure 2-9 shows the calculated properties of guiding mode and its propagating loss on the rib type optical waveguide fabricated on the surface. FIMMWAVE; a commercialized solver of beam propagation method from Photon Design (http://www.photond.com/) was used in calculation. Because BOX thickness of SOI substrate fabricated by low-dose SIMOX is about 100nm, thickness of buried oxide is set to 100nm as shown in Figure. 2-9(a). Figures 2-9(b) and (c) show electric field distribution and propagating loss of optical waveguide in TE mode and TM mode, respectively. From this result there are large propagating loss of 0.31dB/µm (TE mode) and 0.47dB/µm (TM mode) at 1.55µm wavelength light because of the weak confinement in the substrate direction.

- (a) Structure of optical waveguide in simulation

- (b) Electric field distribution of propagating light in TE mode

- (c) Electric field distribution of propagating light in TM mode

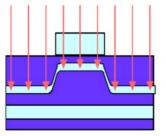

Rickman reported that the minimum thickness of buried oxide is  $0.4\mu m$  to have enough confinement with suppression of substrate radiation of propagating light in silicon optical waveguide.[64] Therefore optical waveguide fabrication method composed of pattern SIMOX process onto an SOI substrate with more than  $0.4\mu m$  thick BOX layer applying the transparent mask in ion implantation is proposed. The simplified process flow is shown in figure 2-10. Figure 2-10(a) oxygen ion implantation is performed onto SOI substrate with  $0.4\mu m$  thick BOX layer through transparent patterned mask. Figure 2-10(b) high temperature annealing creates BOX layer with depth modulation.

Figure 2-10 Optical waveguide fabrication method composed of pattern SIMOX applying the transparent mask

#### 2-6 Features of vertically stacked EPIC

In this section features of EPIC circuits in which CMOS electrical circuits and optical circuits were vertically stacked in thickness direction are described.

Feature 1: Reduction of restrict conditions in layout design

Vertical placement of CMOS electrical circuits and optical circuits expands CMOS electrical circuit area comparing to lateral placement. In case CMOS electrical circuits and optical circuits are placed on the same silicon layer, it is difficult to across the optical circuit area for electrical circuits and to allocate optical waveguide in electrical circuit area. By allocating different silicon layers for CMOS electrical circuits and optical circuits, restrictions in layout designing are dramatically reduced.

## Feature 2: Independent setting of silicon thickness

The suitable silicon thickness for CMOS electrical circuits is getting thinner according to the evolution of CMOS design rule. When CMOS electrical circuits and optical circuits are allocated to different silicon layers, silicon thickness for CMOS electrical circuits can be set to suitable thickness regardless of optical circuit conditions. On the other hand, the silicon thickness of optical circuits can be set to thicker than 220nm which is the thickness of Luxtera's EPIC, so ridge type optical waveguide can be employable.

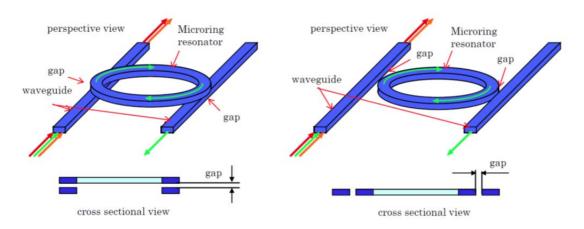

## Feature 3: Availability of vertically stacked optical circuits

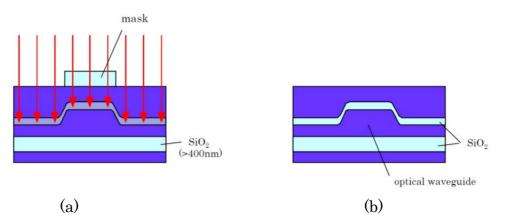

By allocating a part of silicon layer of CMOS electrical circuit area to optical circuits, vertically stacked optical circuits are attainable. Optical coupling between vertically stacked optical waveguides is achieved and multiply aligned vertically coupled micro-ring resonators as shown in figure 2-11 are easily provided.

Figure 2-11 Multiply aligned vertically coupled micro-ring resonators

## 2-7 Experiment of uniform SIMOX on flat SOI substrate

## 2-7-1 Purpose of the experiment

There are some differences between waveguide fabrication into the second silicon layer from surface using SIMOX process on SOI substrate and normal SIMOX process which makes SOI substrate. The differences are written in the followings.

- 1. The substrate on which SIMOX process is applied is SOI.

- 2. There are mask patterns on the substrate in SIMOX.

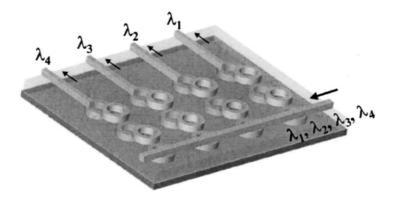

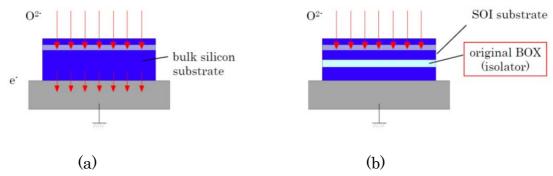

As shown in figure 2-12, when the substrate on which SIMOX process is applied is SOI, implanted charges might be stayed and cause damage by the presence of BOX layer. So this experiment is required. The purpose of this section is to examine the quality of surface silicon layer and uniformity of buried oxide layer when normal SIMOX process which makes SOI substrate for CMOS electrical circuits is applied to SOI substrate.

Figure 2-12 Comparison of SIMOX process in ion implantation (a) normal SIMOX process which makes SOI substrate

(b) fabrication of optical waveguide in second silicon layer from the surface

## 2-7-2 Method of uniform SIMOX on flat SOI substrate

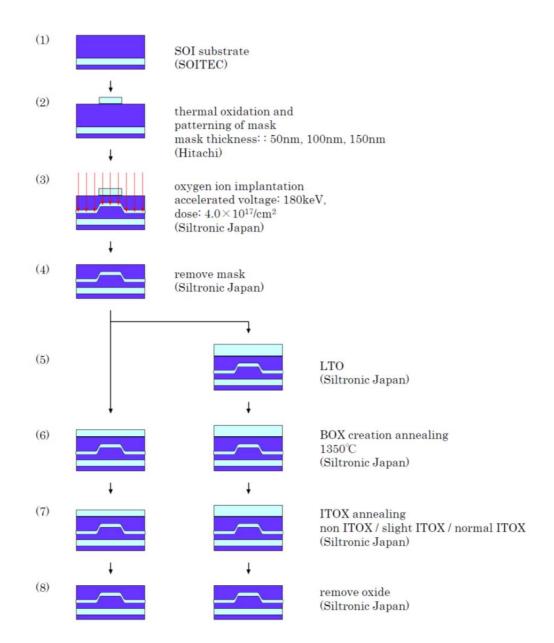

The SIMOX condition of dose of  $4.0 \ge 10^{17}$ /cm<sup>2</sup>, acceleration voltage of 180keV and ITOX [57] is applied in this experiment. Siltronic Japan corporation uses this SIMOX condition in mass production of SOI substrates for CMOS electrical circuits.

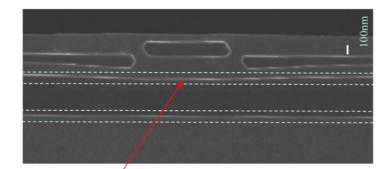

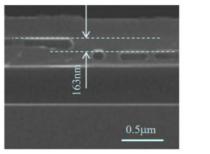

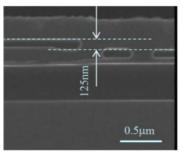

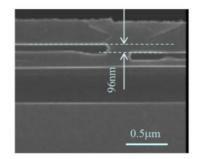

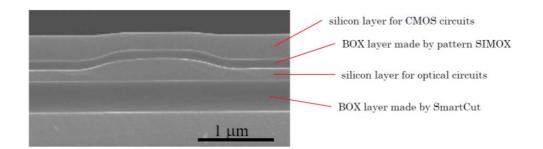

Three types of SOI substrates are used in this experiment. Substrate A: SOI substrate with 700nm of SOI thickness (=top silicon thickness) and 400nm of BOX thickness (= buried oxide thickness) made by SmartCut method at SOITEC, Substrate B: SOI substrate with 700nm of SOI thickness and 150nm of BOX thickness made by SIMOX method at Siltronic Japan, and Substrate C: SOI substrate with 550nm of SOI thickness and 150nm of BOX thickness made by SIMOX method at Siltronic Japan. In addition, normal bulk silicon substrate is used as a reference. SIMOX process (ion implantation and annealing) are adapted by 200mm size SIMOX mass production equipment at Siltronic Japan. SIMOX processes on four silicon substrate (3 SOI and 1 bulk) are implemented at same lot for scrutiny.

Because usual SOI thickness of SOI made by SIMOX with ITOX at Siltronic Japan is 175nm, additional epitaxial growth process is applied on substrate B and C to get 700nm and 550nm SOI thickness, respectively. Parameters and results of substrates are described in table 2-1.

## 2-7-3 Results of uniform SIMOX on flat SOI substrate

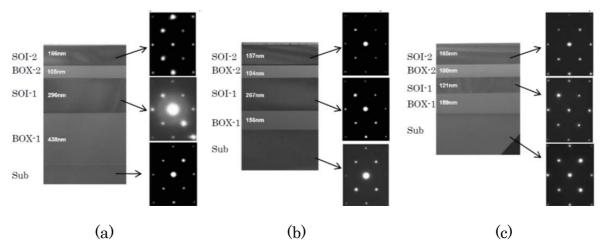

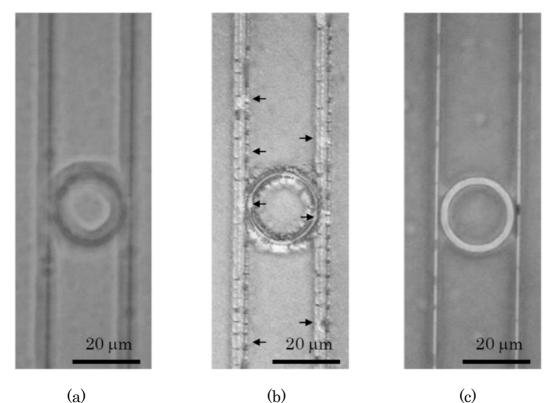

The cross sectional images and diffraction patterns of transmitted electron by transmission electron microscope (TEM) on substrate A, B, and C are shown in figure 2-13 (a) - (c). In these pictures, BOX-1 layer is the original BOX layer and BOX-2 layer is made by this experiment. SOI layer is separated into SOI-1 and SOI-2 by creation of BOX-2. If there are defects in substrate, line shape contrast of pattern will be appeared in TEM images. If there are no disorders in silicon crystal structure, small bright points will be observed in the photograph of diffraction pattern of transmitted electron. The cross sectional images and diffraction pattern of transmitted electron by TEM can evaluate the quality of silicon layers stably.

Additional evaluation by Secco Etching[65] which is one of the quantitative and destructive defect analysis is applied. The original method of Secco Etching was reported by F. Secco d' Aragona in 1972 as a defect evaluation method of silicon substrate. Because the original Secco Etching makes deep pits in silicon layer, it is difficult to evaluate thin silicon layer. Krause, Nakano, and Hemment reported modified evaluation method of Secco Etching[66-68] to evaluate SOI substrate. In this thesis, modified evaluation method of Secco Etching by Hemment[68] is applied in defect analysis as Siltronic Japan applies in mass production.

The results of quantitative and destructive defect analysis on SOI-1; silicon layer for CMOS electrical circuits and SOI-2; silicon layer for optical circuits are shown in table 2-1.

In ITRS (International Technology Roadmap for Semiconductors) published in 2011 corresponding to 22nm CMOS design rule, silicon substrate with defect density of less than  $1.0 \ge 10^{4}$ /cm<sup>2</sup> is regarded as extremely low defect level[69]. In actual design of electrical circuits, compensating circuit is generally prepared for a defect rescue as redundancy[70]. Regarding defect density of less than  $1.0 \ge 10^{4}$ /cm<sup>2</sup> as extremely low defect level shows a substrate with defect density of less than  $1.0 \ge 10^{4}$ /cm<sup>2</sup> has enough quality which does not require additional redundancy. So all substrates have adequate condition in surface silicon layer (SOI-2) for CMOS integrate circuits. Comparing to reference bulk silicon substrate, substrate A has extremely good quality in defect density.

|           | parameters of substrates |             |                            |                          | results of defects den                                           | sity by Secco Etching                                    |

|-----------|--------------------------|-------------|----------------------------|--------------------------|------------------------------------------------------------------|----------------------------------------------------------|

|           | SOI<br>manufacturer      | process     | thickness of<br>BOX-1 (nm) | thickness of<br>SOI (nm) | silicon layer for CMOS<br>electrical circuits(/cm <sup>2</sup> ) | silicon layer for optical<br>circuits(/cm <sup>2</sup> ) |

| А         | SOITEC                   | Smartcut    | 400                        | 700                      | $1.8 \times 10^3$                                                | $> 5 \times 10^{7}$                                      |

| В         | Siltronic<br>Japan       | SIMOX + Epi | 150                        | 700                      | $1.6 \times 10^4$                                                | $> 5 \times 10^7$                                        |

| С         | Siltronic<br>Japan       | SIMOX +Epi  | 150                        | 550                      | $2.0 \times 10^{4}$                                              | > 5×10 <sup>7</sup>                                      |

| reference | Siltronic<br>Japan       | bulk        |                            |                          | $2.7 \times 10^3$                                                |                                                          |

Table 2-1 substrate parameters and results of defect density.

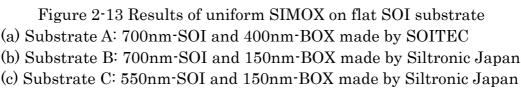

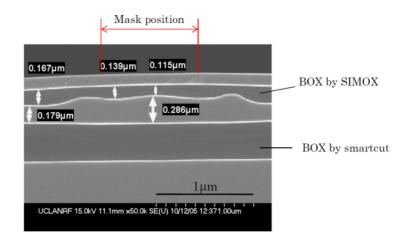

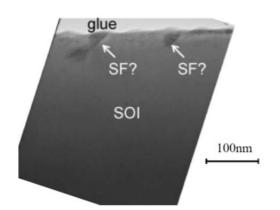

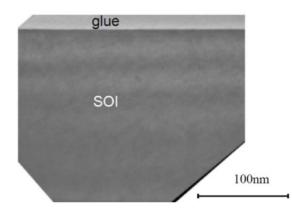

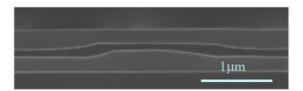

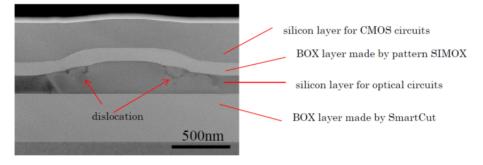

From the cross sectional images and diffraction patterns of transmitted electron by transmission electron microscope (TEM), silicon layer for optical circuits (SOI-1) of substrate A has lower contract. This result shows lattice structure of silicon layer for optical circuits (SOI-1) of substrate A has larger distortion. By further TEM analysis on substrate A, threading dislocation was found as shown in figure 2-14. Although there is a threading dislocation in silicon layer for optical circuits (SOI-1), there is no dislocation in surface silicon layer for CMON electrical circuits (SOI-2). So, defects in SOI-1 and defects in SOI-2 can be regarded as independent. The result that the cross sectional image of diffraction pattern of SOI-1 in substrate A has lower contrast might attribute to that substrate A has thicker BOX-1 layer than substrate B or C.

Figure 2-14 Cross sectional TEM images and diffraction pattern in substrate A.

The experiment of uniform SIMOX on flat SOI substrate in this section reveals that all substrates have adequate condition in surface silicon layer for CMOS integrate circuits (SOI-2) and some defects are created in silicon layer (SOI-1) for optical circuits (SOI-1).

In purchasing high-priced substrate such as SOI substrate, image of X-ray topography[70] which warrants there is no defect of the substrate with non-destructive way can be attached.

Because the distance between SOI-1 and SOI-2 is only 100nm or 150nm which is the thickness of BOX-2, it is impossible to warrant that there are no defects in SOI-2 with image by X-ray topography. The defect observation by optical microscope cannot easily distinguish a defect position in SOI-1 from a defect in SOI-2 because distance of 150nm or 200nm is less than focusing depth.

In order to commercialize EPIC in which CMOS electrical circuits and optical circuits are located on different silicon layer, development of non-destructive defect evaluation method of EPIC substrate is necessary which distinguish a defect in a silicon layer for CMOS electrical circuits, in a silicon layer for optical circuits, or supporting bulk silicon layer. And the non-destructive defect evaluation method of EPIC substrate is to be simplified method which can be adaptable for one hundred percent inspection.

## 2-8 Position of this research

In this research, a production method of SOI substrate which fabricates optical waveguide underneath the surface silicon layer is investigated as a critical technology for commercialization of EPIC. A non-destructive defect evaluation method of EPIC substrate which distinguishes defect among in a silicon layer for CMOS electrical circuits, in a silicon layer for optical circuits, or supporting bulk silicon layer is investigated as an essential technology to make CMOS electrical circuits on the surface silicon layer.

In addition, a memory device which utilizes interaction of SOI transistor and propagating light in optical waveguide underneath the transistor derived from the characteristics of making SOI transistor located immediately above the optical waveguide is investigated.

#### 2-9 Summary

In this chapter, the possibility of pattern SIMOX process to fabricate an optical waveguide underneath the surface silicon layer as a silicon waveguide technology adaptable for CMOS integrated circuits is indicated. The pattern SIMOX process with transparent mask is proposed which avoids creating cracks or defects on surface silicon layer. By the experiment of uniform SIMOX on flat SOI substrate, the defect characteristics that the surface silicon layer has good quality in defect density and there are some defects in silicon layer for optical circuits, are shown. From the defect sensitivity that small defect does not affect property of optical circuits and affects property of CMOS electrical circuits, a simplified non-destructive defect evaluation method which detects the depth of defect position in 0.1micron resolution is required as an essential technology of EPIC. Chapter 3 Non-destructive defect pinpointing by fluorescent microscope

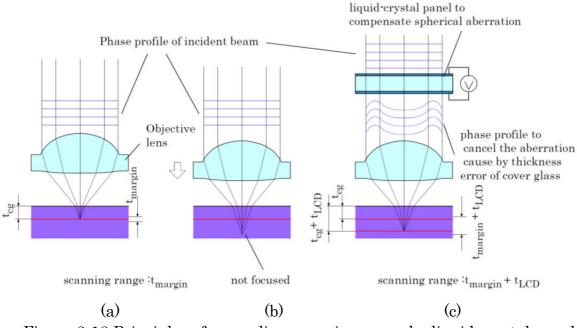

## **3-1 Introduction**

In EPIC substrate which consists of silicon layer for CMOS integrated circuits and silicon layer for optical circuits, an impact of defect depends on the layer where defect exists as shown in figure 3-1. From the experimental results in chapter 2 that defects exist in silicon layer for optical circuits beneath the surface silicon layer with no defect for CMOS circuits, necessity of non-destructive defect examination method which pinpoints the layer where defect exists is indicated.

Figure 3-1 Various impact of defect depends on the layer where the defect exists

X-ray topography[71] has been used in an examination of bulk silicon substrates. X-ray topography indicates the defect without the depth information of the defect. Recently in the examination of SOI substrates, monitoring of UV reflecting laser light from the substrates [72] is used to detect the defects located in the surface region. Although this defect examination method with UV laser light can find defects in surface region non-destructively, this method cannot indicate the defect position in depth direction. Therefore this method cannot determine the defect existing silicon layer in EPIC substrate which consists of silicon layer for CMOS integrated circuits and silicon layer for optical circuits.

In this chapter, non-destructive defect examination method which can

pinpoint the defect with 30nm resolution in depth direction is described. After explanations of an existing defect examination method by fluorescent microscope and computational photography which is the basic technology of this research, proposed non-destructive defect pinpointing method is described. The validation result with pinpointing fluorescent beads on the substrate with 1µm-depth grooves is shown. In addition, method of expanding the measurement range and application of proposing non-destructive defect pinpointing method are discussed.

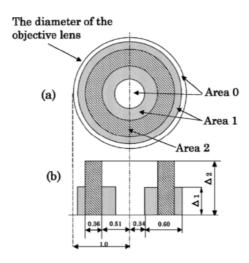

#### 3-2 Existing defect examination method by fluorescent microscope

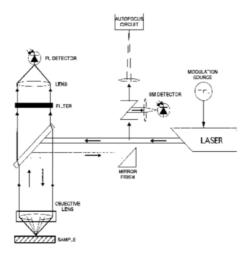

Nevin and Higgs reported the defect examination methods of SOI substrate using fluorescent microscope. [73, 74] Nevin excited defects with 532nm visible laser light and detected the photo-luminescent light with 827nm band emission filter. The fluorescent microsystem which Nevin used is shown in figure 3-2. Although both of exciting light and photo-luminescent light are opaque for silicon substrate, Nevin detected the defects in the depth range from  $0\mu m$  to  $4\mu m$  from the surface. [74]

Figure 3-2 Fluorescent microsystem which Nevin used in defect examination [74] Wavelength of Exciting light and observing light are 532nm and 827nm, respectively.

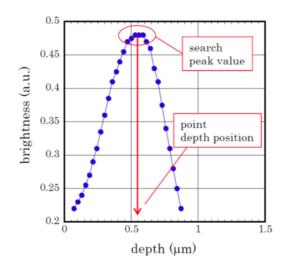

The existing method of detecting the defect depth by fluorescent microscope is discussed. Because the brightness of a defect in fluorescent microscope reaches to the maximum brightness when focusing depth is set to defect position, it is necessary to measure the brightness of photo-luminescent light from a defect during varying the focusing position of the microscope to obtain the defect depth. After obtaining the relation between focusing position in depth direction of fluorescence microscope and brightness of photo-luminescence light from the defects, the position of the maximum brightness indicates the depth of defect as shown in figure 3-3.

In the case of automatic defect examination, image capturing with varying focusing depth and image analyzing of the captured images are performed at each XY position. For example, when defect examination is required to detect the defect in the range from surface to  $2\mu$ m depth with a depth resolution of  $0.1\mu$ m, image capturing with varying the focusing depth with  $0.1\mu$ m step from the surface to  $2\mu$ m depth. However higher NA objective lens is required to detect a defect sensitively, increasing the NA of objective lens reduces the observing area. For example, combination of x40/NA0.8 objective lens and 36mm x 24mm 2D imager with 6 $\mu$ m pixel size captures image area of 0.9mm x 0.6mm with 0.15 $\mu$ m/pixel resolution. When 300mm diameter silicon substrate examination with 20 images

in depth direction at each position is implemented, data size of captured images for one substrate reaches about 9TB even if image data is compressed to JPEG format. So less data size is required in examination with fluorescent microscope.

Figure 3-3 Defect pinpointing method with existing method

As 3D image capturing method with one shot by fluorescent microscope without changing focus position, there are applying spatial light modulator [75, 76], cylindrical lens [77], and quadratically-distorted grating [78]. But these methods reduce capturing area in inverse proportion to number of depth. So required data size in defect examination cannot be reduced.

## 3-3 Deblurring technology with computational photography

In the way of reducing the data size in fluorescent microscopy, deblurring technology with computational photography which creates focused image from blurred image is discussed. Mainstream of deblurring technology with computational photography are lightfield method [79], coded aperture method [80], and extended depth method [81]. Lightfield method is to create focused image by selecting pixel position of image which is captured with applying microlens array in camera system. Coded aperture method is to synthesize the image of rapid moving target by removing blurring from multiple images captured with various apertures at fast rate. Extended depth method is to produce focused image from blurred image which is captured with moving of imager.

In consideration of applying for fluorescent microscope, lightfield method has a disadvantage in image resolution and coded aperture method is not suited for long exposure time imaging. Extended depth method is considered to be fitted for fluorescent microscope with moving of specimen instead of imager.

The concept of extended depth method is that production of focused image is possible if blurred condition is given. The camera system which Nayar performed extended depth [81] is shown in figure 3-4. Nayar moves image detector during exposure in focus direction. Figure 3-5 shows (a) captured image and (b) produced image. Figure 3-5(a) has blurring in all area because imager was moving during exposure. By analyzing blurring condition as a function of pixel position, focused image as shown in figure 3-5(b) was produced.

Extended depth method makes it possible to produce focused images of both targets in near position and targets in far position at the same exposure. So extended depth method is regarded as the method which can reduce image capturing number because this captures focused images of the targets which cannot be captured at the same exposure.

Figure 3-4 Camera system which Nayar performed extended depth [81]

(a) Captured Image (f/1.4, T=0.36sec)

(b) Computed EDOF Image

Figure 3-5 Images of extended depth method by Nayar. [81] (a) captured image (b) produced focused image

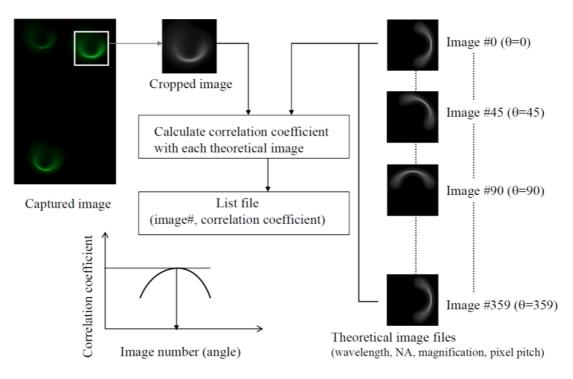

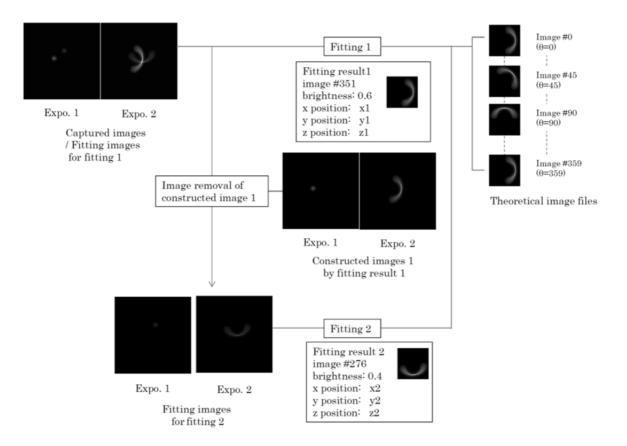

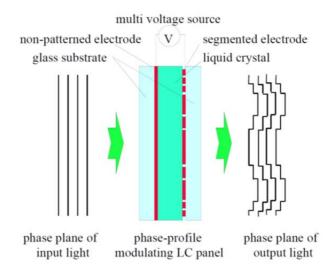

## 3-4 Proposed imaging method

The imaging target in this research is a defect in silicon substrate. From the experimental results in chapter 2, the densities of defects in silicon layer for CMOS electrical circuits and in silicon layer for optical circuits are less than 1.0 x $10^{4}/\text{cm}^{2}$  and less than  $5.0 \text{ x} 10^{7}/\text{cm}^{2}$ , respectively. Image capturing area with the combination of x40 objective lens and full size imaging device (36mm x 24mm) is 0.9mm x 0.6mm. The number of defects in this image capturing area in silicon layer for CMOS electrical circuits and optical circuits are less than  $5.40 \text{ x} 10^{1}$  and  $2.7 \text{ x} 10^{5}$ , respectively. Because these numbers are two digits smaller than the number of pixels in imager;  $2.4 \text{ x} 10^{7}$ , targets in captured image are sparse. There might be enough spaces around defect in captured image by fluorescent microscope. The author thought that there might be enough space for blurred image with depth information, and consequently image capturing number might be reduced.

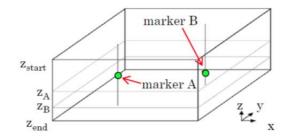

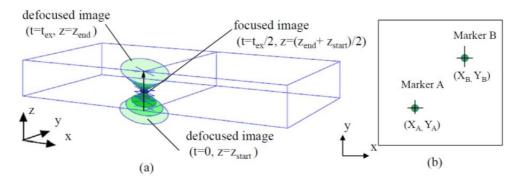

The proposed method is described using the 3D space shown in figure 3-6. There are two target markers A and B between  $Z_{\text{start}}$  where is the start position of

exposure, for example the surface, and  $Z_{end}$  where is the end position of exposure, for example  $Z_{end}$  depth position from the surface. The position of marker A and B in depth direction are  $z_A$  and  $z_B$ , respectively. And both  $z_A$  and  $z_B$  are located between  $Z_{start}$  and  $Z_{end}$ , and  $z_A$  is located almost center of  $Z_{start}$  and  $Z_{end}$  and  $z_B$  is located near  $Z_{end}$ .

Figure 3-6 3D space for proposed method discussion

The proposed method is composed of following two exposure process.

The movements of mechanical stages of specimen in the first exposure are expressed in the equations from eq. 3-1 to eq. 3-3. X and y stages are fixed during exposure time:  $t \ (0 \le t \le t_{ex})$  and z stage is moved from  $z_{start}$  to  $z_{end}$  at constant speed.

Figure 3-7(a) presents the movement of projected image of marker A on imaging devices, and figure 3-7(b) presents the recorded image. At the beginning of exposure (t=0) focus plane is not on marker A, and image of marker A on imaging device is defocused. At  $t = 1/2t_{ex}$ , focus plane is on marker A, and image of marker A on imaging device is focused, so image of marker A on imaging device has the maximum brightness and the smallest area. At the end of exposure (t= t<sub>ex</sub>) focus plane is not on marker A, and image of marker A on imaging device is defocused. However the recorded images of marker A and B through the first exposure have blurring comparing to focused images, the x and y positions of marker A and B can be recognized because x and y stages are fixed. The first exposure step is to recognize x and y positions of the targets.

$$z(t) = z_{\text{start}} + (z_{\text{end}} - z_{\text{start}}) \frac{t}{t_{\text{ex}}}$$

(Eq. 3-1)

$x = x_0$  (Eq. 3-2)

$y = y_0$  (Eq. 3-3)

Figure 3-7 Description of the first exposure step of proposed method (a) movements of projected image of marker A on imager (b) recorded image

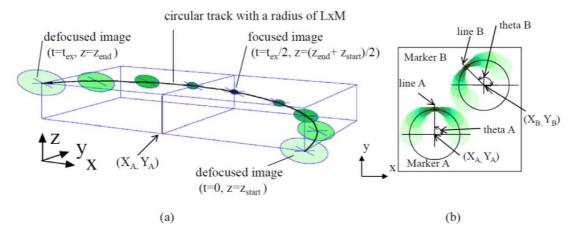

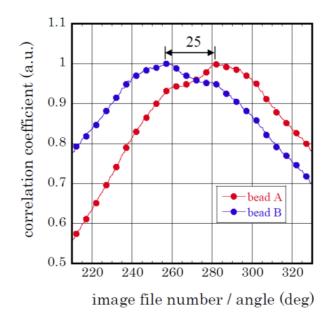

The movements of mechanical stages of specimen in the second exposure are expressed in the equations from eq. 3-4 to eq. 3-6. Z stage is moved from  $z_{start}$ to  $z_{end}$  at constant speed as same as the first exposure. X and Y stages are moved synchronously on the circular track with radius L at constant angle velocity. Figure 3-8(a) presents the movement of projected image of marker A on imaging devices, and figure 3-8(b) presents the recorded image. At the beginning of exposure (t=0) focus plane is not on marker A, and image of marker A on imaging device is defocused. At t =  $1/2t_{ex}$ , focus plane is on marker A, and image of marker A on imaging device is focused, so image of marker A on imaging device has the maximum brightness and the smallest area. At the end of exposure (t=  $t_{ex}$ ) focus plane is not on marker A, and image of marker A on imaging device is defocused. Because x and y stages are moved synchronously with z stage in the second exposure, the projected image of marker A on imaging device is moved on the circular track with the radius of L multiplied with optical magnification of microscope M. The recorded images of marker A and B expresses the circular movement of stages along with blurring information as shown in figure 3-8(b).

By the comparison of equations 3-2, 3-3 and 3-5, 3-6, the center of circular image of marker A and B in figure 3-8(b) is the position of image of marker A ( $X_A$ ,  $Y_A$ ) and B ( $X_B$ ,  $Y_B$ ) in figure 3-7(b). By drawing the lines from positions of marker A ( $X_A$ ,  $Y_A$ ) and B ( $X_B$ ,  $Y_B$ ) to the focused point of recorded circular images of marker A and B,  $\theta$  presents the time when focus position is located at marker position. From the reason that z stage moves at constant speed, time focus position is located at marker position indicates the depth position. The second exposure step is to measure z positions of the targets.

Therefore 3D positions of marker A and B can be pinpointed by analyzing two images captured by proposed method.

$$\begin{aligned} z(t) &= z_{\text{start}} + (z_{\text{end}} - z_{\text{start}}) \frac{t}{t_{\text{ex}}} & \text{(Eq. 3-4)} \\ x(t) &= x_0 + L \times \cos\left(\pi \frac{t}{t_{\text{ex}}}\right) & \text{(Eq. 3-5)} \\ y(t) &= y_0 + L \times \sin\left(\pi \frac{t}{t_{\text{ex}}}\right) & \text{(Eq. 3-6)} \end{aligned}$$

Figure 3-8 Description of the second exposure step of proposed method (a) movements of projected image of marker A on imager (b) recorded image

#### 3-5 Experiment for verification

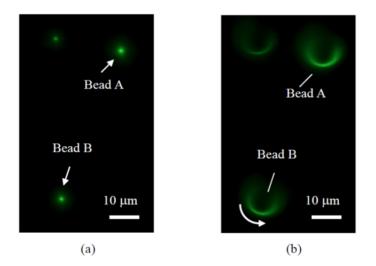

The experiment for verification of proposed method to pinpoint 3D positions of marker by two exposure process is described.

In this experiment, fluorescent beads with uniform diameter are used to verify the accuracy of pinpointing depth.

#### 3-5-1 Experimental setup and specimen

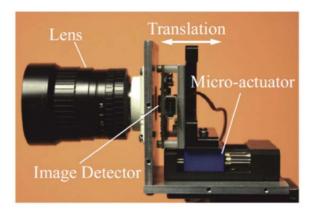

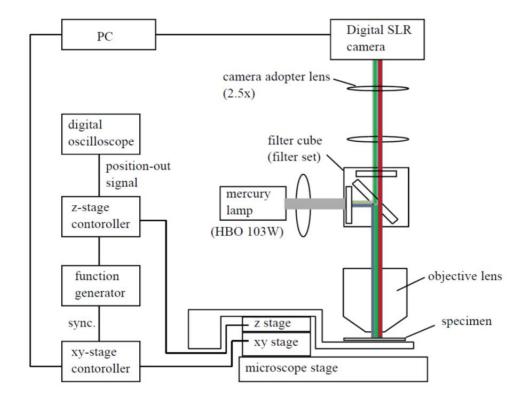

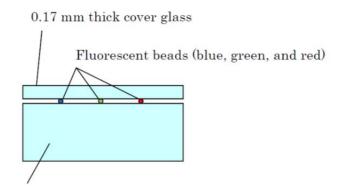

Experimental setup is shown in figure 3-9. An FOV type fluorescent microscope (Axio Imager Z1 made by Carl Zeiss) is used. A piezo type x and y stage (P-628K001 made by Physik Instrumente) and a piezo type z stage (P-622.ZCL made by Physik Instrumente) are placed on the specimen stage of the microscope to perform x, y, and z movement of specimen. X and y stage and z stage are controlled by closed loop system using x and y stage controller (E-710.4CL made by Physik Instrumente) and z stage controller (E-661CP made by Physik Instrumente) and z stage controller (E-661CP made by Physik Instrumente), respectively. The target position of z stage is set by function generator synchronized with x and y stage controller. DSLR camera (Alpha 900 made by Sony Corporation) is attached to fluorescent microscope through 2.5x image conversion lens (Carl Zeiss). The DSLR camera has 24.81M pixels CMOS imager whose pixel size is  $5.94\mu$ m. Both DSLR camera and x and y stage controller are directly controlled by PC.

The control signals for target position of x and y stage are sinus function and phases of these signal have difference of 90 degrees to get circular movement of specimen. The amplitude and frequency of sinus function are of 5 $\mu$ m and 0.2Hz, respectively, and specimen is moved on circular track of 5 $\mu$ m radius and its angle velocity is 72deg/sec. 20x objective lens (Plan-APOCHROMAT 20x/0.8, Carl Zeiss) is applied in the fluorescent microscope. The combination of 20x objective lens and 2.5x conversion and 36.2mm x 24.1mm 2D imager captures image area of 724  $\mu$ m x 482  $\mu$ m. In addition, specimen moves on 5 $\mu$ m radius circular track, imaging area is reduced to 714  $\mu$ m x 472  $\mu$ m by this circular movement.

In case the speed of z stage is set to  $3\mu$ m/sec and exposure time is set to 4sec, scanning distance in depth is  $12\mu$ m. Although the specifications of position accuracy of x, y, and z stages are 10nm, position accuracy of z stage is about 50nm because of existence of 200kHz vibration measured by stage feedback signal.

Figure 3-9 Experimental setup

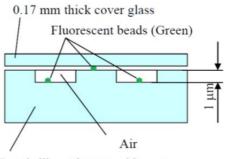

Fused silica substrate with grooves

Figure 3-10 Specimen structure

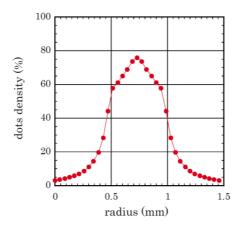

A specimen structure is shown in figure 3-10. The material of substrate of specimen is fused silica and there are groove structures at the surface of substrate. A green color fluorescent beads of  $0.3\mu$ m diameter (Fluoro-max G300 made by Thermo Fisher Scientific) are randomly placed on the substrate. A 0.17mm thick cover glass is placed because the objective lens is designed with 0.17mm cover glass. The depth of groove was 1.00 $\mu$ m measured by surface profile meter (P10 made by KLA Tencor).

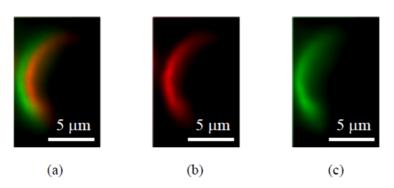

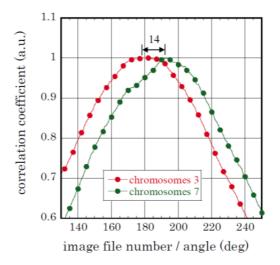

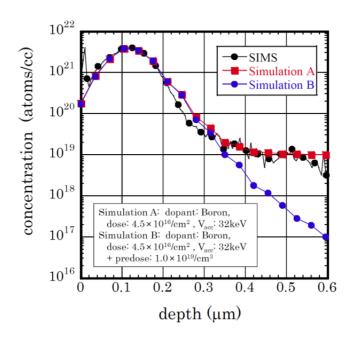

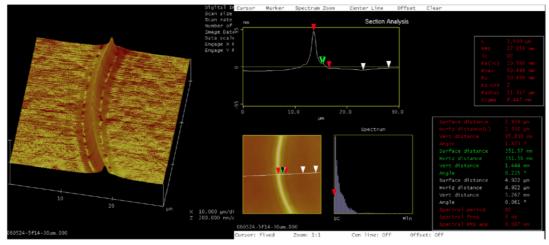

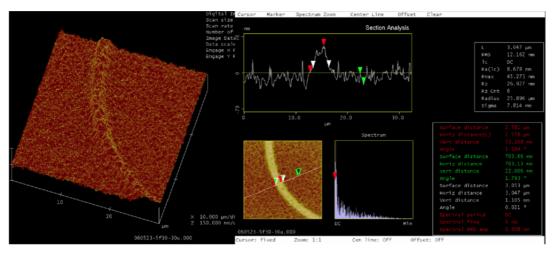

# 3-5-2 Verification result